纠错还是速度?IBM发布超1000量子比特量子计算机,或改变发展路线

发布时间:2024-01-10

5259 墨子沙龙

作者 | 尹璋琦,北京理工大学

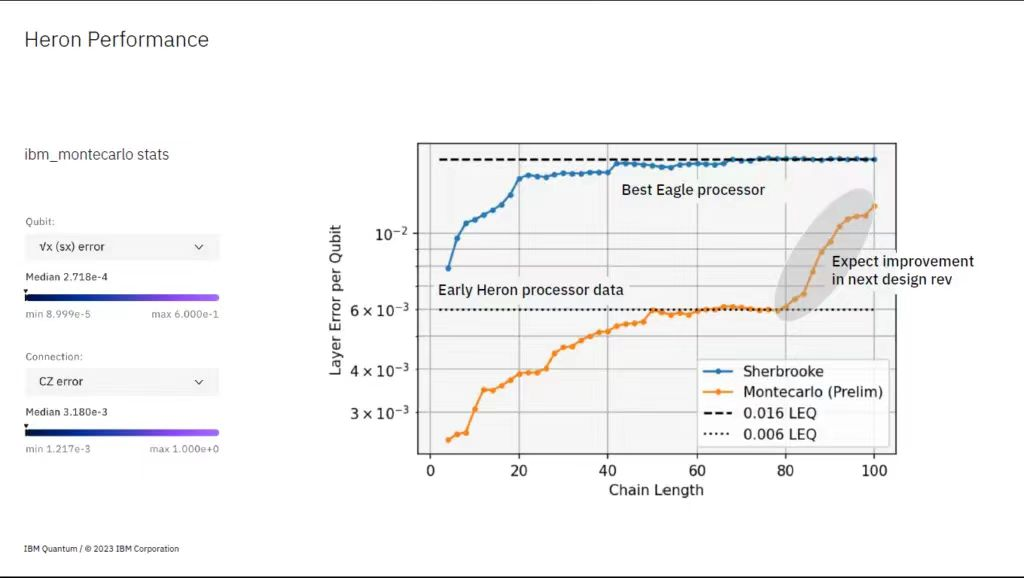

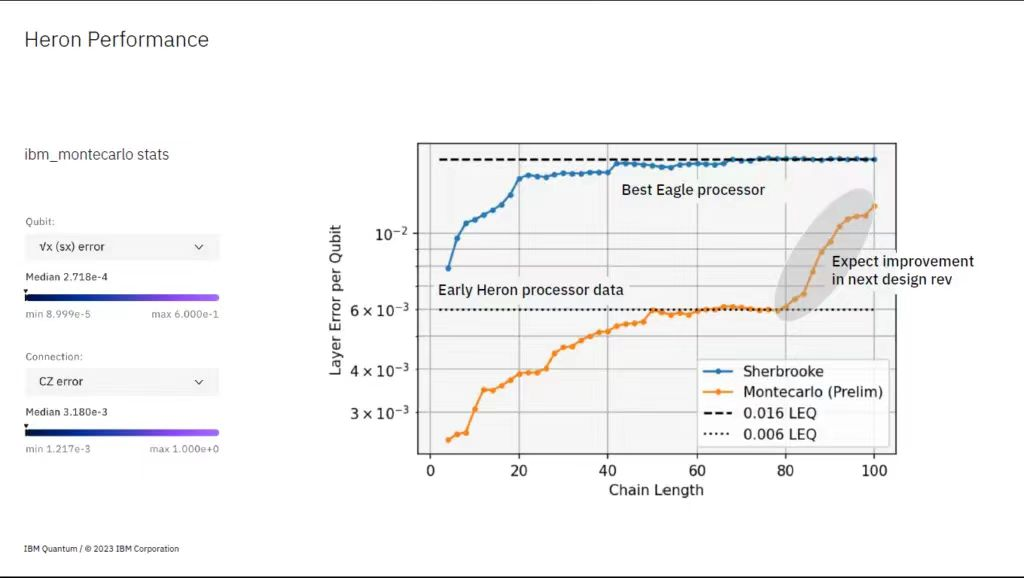

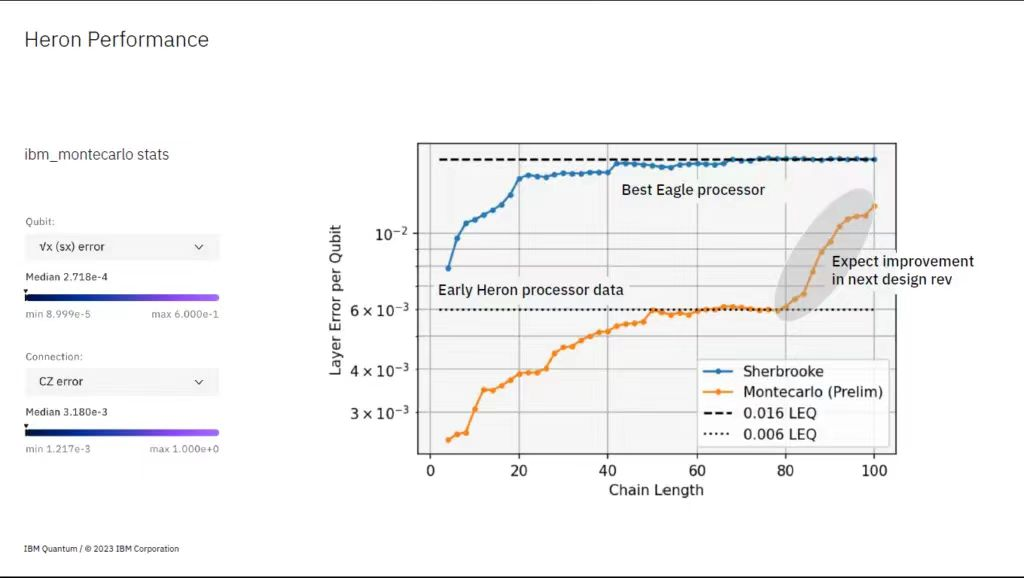

2023年12月4日,美国IBM公司发布了包含1121个量子比特的Condor(秃鹰)超导量子处理器(QPU)。在超导量子计算机的发展路线中,规模(量子比特数目)、速度和容错率是最重要的几个指标。秃鹰超越1000个量子比特的规模为提高量子计算机的容错能力提供了可能性。因为如果想要利用表面码纠错方式实现一个纠错阈值最高达1%的容错逻辑量子比特,1000个物理量子比特的规模可以说是“起步价”。因此,包含1121个量子比特的“秃鹰”,无疑展示了IBM想要在容错率方面展现实力的野心。不过秃鹰量子处理器的性能并未公布,是否超越纠错阈值还未可知。然而,要达到千比特的规模,IBM必须付出“代价”。量子处理器之间使用量子接口连接,还需要用电缆来连接不同的制冷机,这些接口和电缆都会减缓处理器的速度。此外,为了避免量子比特之间的串扰,处理器之间的连通性(连通性与QPU里每个量子比特能直接耦合到临近量子比特的数目相关)也必然受到影响,更加降低了系统整体工作的效率。所以,我们还需要等待IBM提供更多的实验数据,来评估千比特的量子处理器最终的整体运算能力。在发布秃鹰量子处理器的同时,IBM还发布了性能更高,但量子比特数只有133个的Heron(苍鹭)量子处理器。从下图可以看出:苍鹭量子处理器的单量子比特量子门错误率中位数为万分之2.718,双量子比特控制Z门错误率中位数为千分之3.18。在超过100个量子比特的超导量子计算系统中,仍能保持如此低的错误率,IBM的技术确实处于世界领先。

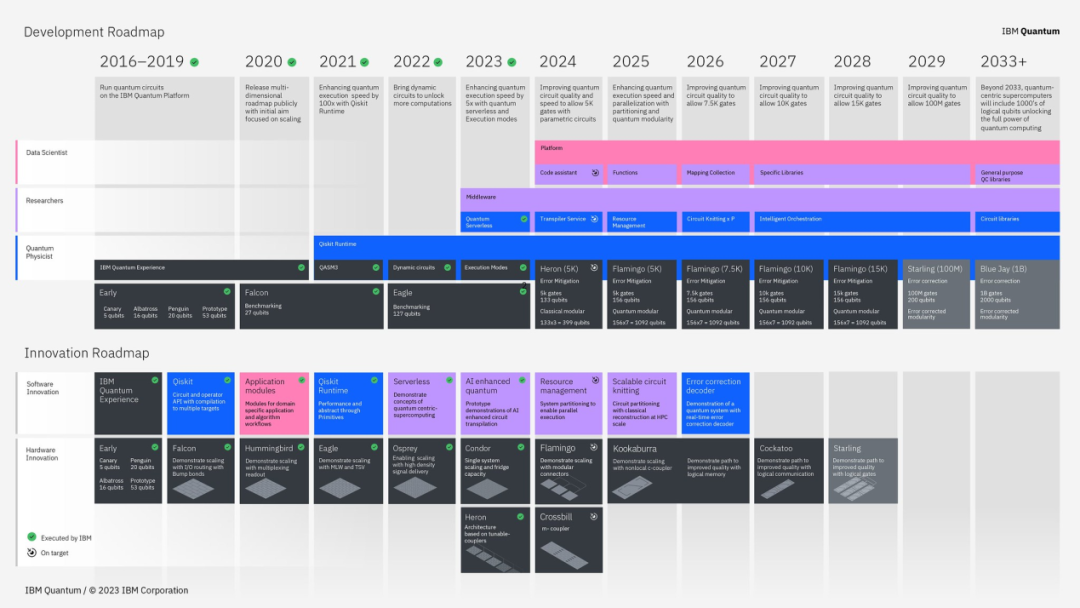

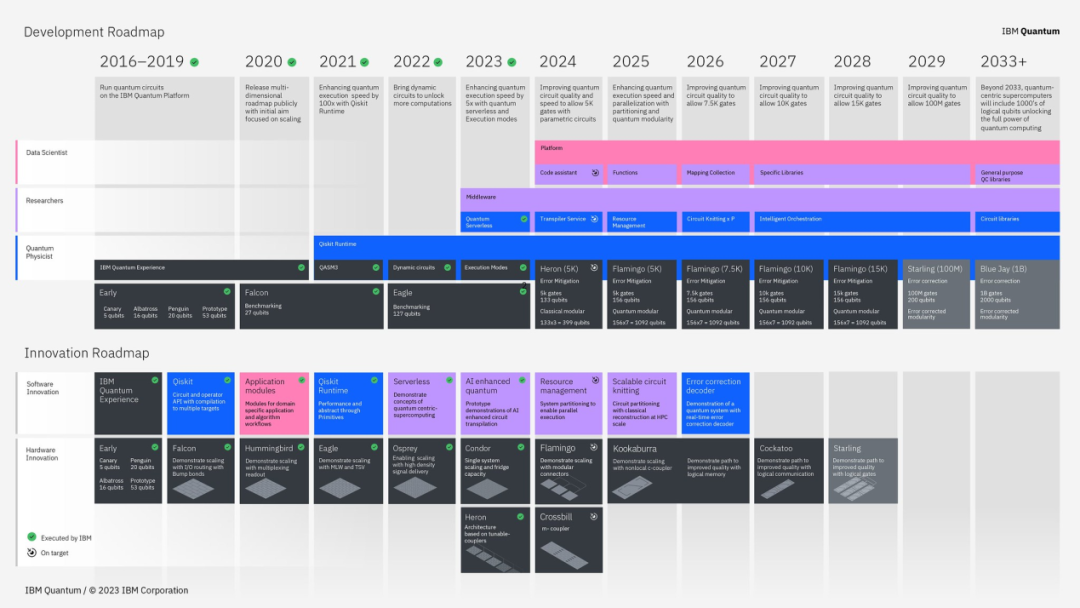

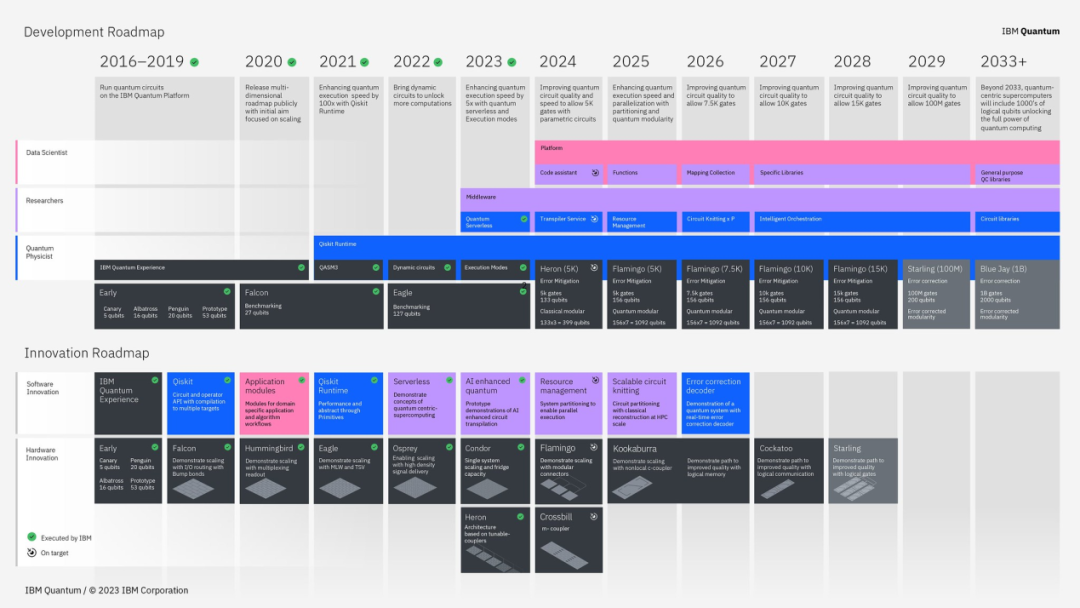

量子硬件进步的同时,IBM在量子纠错码设计方面也有新的理论突破。众所周知,近年来,一种新出现的量子纠错方案——量子低密度奇偶校验码(quantum low-density parity check code,QLDPC),引起了研究人员的兴趣。而根据IBM今年的一篇论文的研究结果,相比表面码,QLDPC物理量子比特资源的消耗降低一个量级以上——也就是说,利用表面纠错码实现一个逻辑量子比特需要1000个物理比特,而利用QLDPC校验码只需要100个物理量子比特就够了,同时还能维持逻辑量子比特的纠错阈值基本不变。当然,新的技术都有两面性,要使用QLDPC校验码,需要在量子比特之间引入非紧邻的耦合——这对超导量子计算系统的实际验证带来了极大的挑战。要按照此技术路线实现容错量子计算,量子处理器硬件电路设计需要推倒重来,量子计算发展路线图也要随之调整。事实上,根据IBM公司的新闻稿,我们确实能看到路线图重绘的迹象。2020年,IBM公司发布了第一张量子计算发展路线图,预计将于 2023 年发布1121个量子比特的秃鹰量子处理器。2022年,IBM更新了路线图,计划创建新的量子处理器、软件和服务,同时增加了2023 年推出133 量子比特苍鹭量子处理器的新计划。而此次秃鹰量子处理器和苍鹭量子处理器能如期发布,充分体现了IBM公司精准的规划能力和雄厚的技术实力。此次发布新量子处理器的同时,IBM公司又一次更新了量子计算路线图,如下图所示。

整体来看,与上一版路线图相比,新版路线图技术参数细节更具体,也更具有可行性:不仅指出了量子比特数目,还标明了容错量子逻辑门数目。相对来说,新版路线图中,2028年之前的目标参数指标非常具体:量子处理器中量子比特数维持在156个,容错量子门次数提升到15000,把7个处理器链接起来,可实现1092个量子比特的处理器。而2029年及之后的参数指标则比较模糊:可实现超过108个容错量子门和超过200个量子比特的处理器。难点在于,短短一年时间,容错量子门数目从15000提升到108,4个数量级的跨越如何实现?关于这一点,IBM没有提供技术细节。在笔者看来,IBM必须要发展量子低密度奇偶校验码等新型量子纠错技术,大幅度降低量子逻辑门的错误率,同时减少对物理量子比特的消耗,才有成功的希望。从上图我们还可以看出,从2023年开始的5年内,IBM量子计算发展的核心目标并不是扩大量子比特的规模,而是在维持156个量子比特数的基础上,希望不断提升量子门的可靠性,这也体现了他们发展容错量子计算的决心。中国科大、浙大、清华、南方科大和北京量子院等单位超导量子计算团队,各自独立设计并制备了量子比特数50到100个的量子处理器,同时对瞄准量子门保真度和量子态测量保真度等关键指标进行攻关,量子门的错误率已经降低到0.5%左右。此外,假定纠错阈值已经达到的前提下,码距是实现纠错码必须要考虑的一个关键参数。码距是一种“用空间换准确性”的方案,纠错码中码距越大,能够纠正的错误率就会越大。原理上,码距等于通过纠错码能够纠正物理量子比特中发生错误个数的两倍加1。所以,要让纠错码起码能纠正一个错误,码距至少要达到3。中国科大的团队瞄准表面码纠错开展攻关,在2022年7月首次实现了码距为3的表面码纠错码,并展示了表面码的探错和纠错过程。2023年11月他们又基于表面码实现了快速、高保真的逻辑魔法态制备。然而,进行量子纠错操作也可能带来额外错误,导致实际使用量子纠错时得不偿失。想要量子纠错产生正向收益,必须让量子纠错操作之后的逻辑量子比特相干性超过原始的物理量子比特相干特性。通俗的来说,就是让纠错后的逻辑比特相干性寿命更长,工作更久,从而实现超过“盈亏平衡点”。

2023年3月,南方科技大学深圳量子科学与工程研究院联合福州大学、清华大学等团队,通过实时重复的量子纠错技术,延长了逻辑量子比特的相干寿命,达到了 805 微秒,超过了该系统中不纠错情况下最好的物理比特的相干寿命(694 微秒),超越了“盈亏平衡点”。这些工作为通用和可扩展的容错量子计算奠定了重要基础。笔者相信,按照这样的发展趋势,2030年之前,我国也有希望实现容错量子计算。